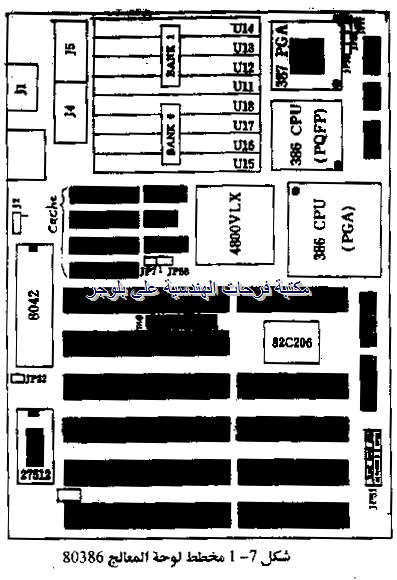

اللوحة الأم للمعالج 80386

نتناول في هذا الفصل شرح اللوحة الأم للمعالج 80386 يبين شكل 1-7 مخطط لنموذج لوحة نظام 80386 وبالنظرة الأولى لن نجد اختلاف كبير عن لوحة المعالج 80286 ويمكن أن نلخص مواصفات هذه اللوحة كما يلي: أسفل اللوحة ناحية اليمين يوجد اثنين Socket يستخدم أحدهم لتثبيت المعالج وحسب نوعه. فأحدهم للمعالج 80386 إن كان ذو تغليف من النوع PGA وتعني Pin Grid Array أي الأطراف موزعة في شكل مصفوفة عند إضلاع المعالج الأربعة، حيث المعالج يأخذ الشكل المربع ، بينما الـ Socket الثانية للمعالج 80386 إن كان ذو تغليف PQFP وتعني Plastic Quad Flat back Package وفي هذه الحالة يكون المعالج مسطح الشكل وأطرافه ملحومة على لوحة مطبوعة صغيرة (Kit)، ولهذه اللوحة أرجل هي التي تثبت في الـSocket. المعالج 80386: يتميز المعالج 80386 بأن سعة ناقلة بياناته 32بت، وهو صورة محسنة لكل من المعالجات 80286, 8086, 8088 الذي سعة ناقلة بياناته 16 بت. ومن سمات هذا المعالج الآتي: · تنفيذ عدة أعمال في وقت واحد Multitasking. · إدارة الذاكرة Memory Management. · الذاكرة الافتراضية Virtual Memory. · حماية البرامج Software Protection...