دائرة الوصول المباشر للذاكرة dma:

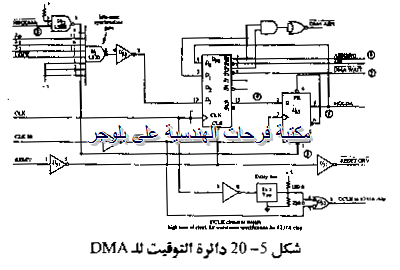

تتكون دائرة الـ dma في الحاسب ibm pc-xt من الرقاقات u51, td1, u52, u99, u18, u19, u17, 8237a (u35) تستخدم القناة channel 0 منفردة لإنعاش الذاكرة ram بينما القنوات الثلاث الأخرى للرقاقة channel 2, channel1 channel3 8237 فهي تستخدم لعمليات نقل 0 dma وطبعاً قبل القيام بأي عملية dma يجب تمهيد أو برمجة الرقاقة 8237 بواسطة المعالج الدقيق. ويمكن الوصول لمسجلات 8237 الداخلية بواسطة أوامر الـ (1/0 instructions) 1/0 فعناوين 8237 في المدى 000h-00fh فعند العنونة بأي من هذه العناوين فإن الطرف 11 للرقاقة 8237 سيكون منخفضاً ومنشطاً للخط dmacs كما هو مبين في شكل 19-5

وعندما يكون dma cs فعالاً ومعه xiow أو xior فإن المعالج الدقيق يصل لأحد المسجلات الداخلية للرقاقة u35 فيما يلي تسلسل عمل الدائرة استعن بالشكلين (20-5 19-5).

1- تنشيط أحد الخطوط rq0-drq2 يبدأ 8237 دورة.

2- تنشيط الخط hrq dma عند الطرف 2 بالرقاقة u99 والطرف 2 بالرقاقة u52.

3- ما سبق يؤدي إلى تحرير خط المسح للقلاب بالرقاقة u67 فيعمل على تنشيط خرج القلاب (الخط holda) فيدخل هذا الدائرة حالة انتظار حتى يدخل المعالج الدقيق حالته الغير فعاله.

4- وبمجرد أن يدخل المعالج الدقيق حالته الغير فعاله فإنه يرفع خطوطه lock, s2 s1, s0 بسبب هذا تدخل إشارة إلى القلاب 3 بالرقاقة u98 من خلال البوابة u5 ثم u83 مما يرفع خط الخرج q 3 عند الطرف (u98) 15 إلى منطق عالي وذلك لحظة حافة الصعود للإشارة clk.

5- وعند لحظة حافة الهبوط لنبضة الساعة فإن الطرف 5 بالرقاقة u67 (الخط hold) وهو مخرج القلاب يتم وضعه (set) وتشير هذه الإشارة لحاكم الـ dma بأن الناقلات أصبحت تحت سيطرته.

6- عند لحظة حافة الصعود الجديدة لنبضة الساعة فإن الطرف 2 (خط الخرج q0) للرقاقة u98 يصبح فعالاً وهو يمثل الإشارة aen brd وتقوم هذه الإشارة بإطفاء الوحدات الوسيطة لناقلة المعالج وبالتالي تحرير الناقلات.

7- وعند الدورة التالية فإن الخرج q1 (الطرف 6) بالرقاقة u98 وهو الإشارة dma wait تصبح فعاله (منخفض) يسبب هذا دخول المعالج حالة انتظار إضافية قبل انتقاله إلى حالته الغير فعالة ويقوم المعالج بإشعال الوحدات الوسيطة لناقلة الـ dma وهي الرقاقات u19, u18, u17

8- يرسل حاكم الـ dma إشارة لجهاز الـ 1/0 وذلك برفع منطق الخط dack.

9- يسبب ما سبق أن الجهاز يخفض منطق الإشارة dreq وعند هذه اللحظة يكون حاكم الـ dma له السيطرة على الناقلات.

10- يخفض حاكم الـ dma منطق الخط ior.

11- عند دورة dclk الجديدة فإن حاكم الـdma يخفض الخط write وعند هذه اللحظة يكون قد تم نقل واحد بايت.

12- عند دورة dclk جديدة فإن حاكم الـ dma ينفذ حالة انتظار واحده وعند دورة dclk تالية فإن حاكم الـ dma يرفع منطق كل من الخطين hrq dma, memw.

13- يبدأ منطق حاكم الـ dma في تحرير الناقلات 0 تكون دورة dclk التالية هي الدورة الأخيرة، عندها يرفع حاكم الـ dma منطق الخط ior.

وحيث أن حاكم الـ dma المستخدم هنا يتحكم في ناقلة عناوين ذات 16-bit فقط، لذا يستخدم مع هذا الحاكم رقاقة ram ذات 4-bit x 4- كما هو موضح بشكل 21-5 وتسمى هذه الرقاقة Page RAM أو segment RAM وهي برقم كودي 74LS670 وتكون في الموقع U19 وتستخدم لتخزين الـ 4-bit العلوية من العنوان. ويتم برمجتها بواسطة المعالج الدقيق لتحديد أي قطاع 64-kb من الذاكرة هو الذي سيستخدم في عملية الـDMA Transfer . وحيث أن Channel 0 خصصت لإنعاش الـ RAM فإنه يمكن الوصول فقط لثلاث قنوات تعنون كلاً القناتين Channel 1, Channel 0 الموقع. من الـPage RAM بينما القناة Channel 2 تعنون الموقع 2 لأن DACK متصل بالـ bit الأقصى أهمية من عنوان الـ (RB) page RAM كما هو مبين بشكل 21-5

تعنون القناة Channel 3 الموقع 1 لأن DACK متصل بالـ bit الأدنى أهمية من عنوان الـ (RA) page RAM لا يتم استخدام الموقع 3 في الـ page RAM فهو مهمل.

يمكن للمعالج الدقيق برمجة الـ DMA page بواسطة كتابة موقع 1/0 التي عناوينها في المدى 80H-83H ولكن لا يمكن له إعادة قراءتها ويتم هذا عندما يقوم المعالج بعملية الكتابة بـ 1/0 في مدى العناوين السابق عندما يتم اختبار Y4 (الطرف 11 في فاكك الشفرة U66) ويكون أيضاً XIOW فعالاً فإنهما يجعلان الطرف 11 للبوابة U15 فعالاً وبالتالي تتولد الإشارة WRT DMAPG REG للـpage RAM كما هو مبين في الشكل 22-5.

ستقوم الإشارة DMA AEN بإخراج البيانات من Page RAM الآن سيتم وضع الـ 4-bit المعنونة بواسطة قناة الـ DMA على الخطوط 0A16-A19 وكما نرى من دائرة الـ DMA أنه لا توجد وسيلة لتغيير محتويات الـ page RAM بعد برمجتها بواسطة المعالج لذلك فإن عملية الـ DMA محدده فقط بقطاع واحد من الذاكرة (64-kb) لا يمكن تخطيه.

تعليقات

إرسال تعليق