رقاقة حاكم الناقلة (Bus Controller) 8288

عندما يعمل المعالج الدقيق بأسلوب الـ Maximum Mode فإنه يجب أن يستخدم رقاقة حاكم الناقلة 8288 لتتولي هي إصدار إشارات التحكم نيابة عن رقاقة المعالج الدقيق، حيث تم إلغاء إشارات التحكم من المعالج الدقيق بوضعه (Set) عند أسلوب الـ Maximum 0 Mode ويسمح تشغيل المعالج الدقيق 8088 في الحاسب IBM PC-XT باستخدام المعالج المساعد 8087 اختيارياً ويبين شكل 4-30 المخطط الصندوقي

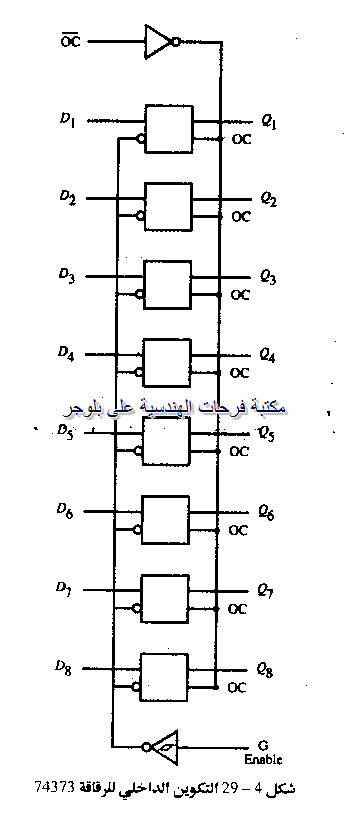

لرقاقة حاكم 8288، بينما يبين شكل 4-29 تعريف أطراف هذه الرقاقة.

يقوم بلوك فاكك شفرة الحالة Status decoder بفك شفرة خطوط الحالة S2,S1,S0 كما هو مبين في جدول الحقيقة التالي:

يقوم بلوك منطق التحكم Control Logic بتحديد الأمر الذي سيتم إصداره، ويتولى بلوك مولد إشارة الأمر Command Signal Generator بإصدار الأمر الجدول التالي يبين مجموعة أوامر الخرج.

ويتصل بلوك مولد إشارات التحكم Control Signal Generator بكل من وسيط/ سقطة العنوان ومرسل/ مستقبل البيانات وإشارات تحكم المقاطعة. وإشارات خرج مولد إشارات التحكم كما يلي:

ووظائف إشارات رقاقة حاكم الناقلة 8088 كالأتي:

1- Vcc (Pin 20): طرف تغذية +5 volts

2- GND (Pin 10): طرف تغذية (الأرضي).

3- S2 (Pin 18), S1 (Pin 3), S0 (Pin 19) هي إشارات دخل الحالة Status Input Signals ويتم فك شفرة هذه الإشارات بواسطة الرقاقة 8288 لتوليد إشارات ناقلة التحكم كما هو مبين بجدول الحقيقة السابق.

4- CLK (Pin 2): هي إشارة دخل الساعة وتأتي الرقاقة 8288 وتقوم هذه الإشارة بتوقيت تحكم الناقلة Bus-Control Timing.

5- AEN (Pin 6): إشارة تمكين العنوان وتقوم بإخبار 8288 بأن تصدر إشارات تحكم الذاكرة Memory-Control Signals

6- CEN (Pin 16): إشارة تمكين لأمر Command Enable Signal وهي تقوم بالتحكم في كل مخارج الأمر وكذلك تتحكم في المخارج PDEN, DEN فعندما تكون CEN منطق عالي فإن إشارات الأمر/التحكم يتم إصدارها بينما عندما تكون CEN منطق منخفض فإنه يتم عدم تمكين هذه الإشارات.

7- IOB (Pin 1): إشارة أسلوب دخل/خرج الناقلة Input/Output Bus Mode Signal فعندما تكون هذه الإشارة منطق عالي فإن 8288 يكون في أسلوبه ناقلة (1/0 Bus Mode) 1/0 بينما عندما تكون هذه الإشارة عند منطق منخفض فإن 8288 يكون في أسلوب النظام (System Bus Mede) ويستخدم أسلوب الـ 1/0 عندما يكون هناك ناقلات منفصلة متاحة لكل من الـ 1/0 والذاكرة. ويستخدم أسلوب ناقلة النظام عندما يشترك كل من الـ1/0 والذاكرة في إشارة ناقلة واحدة.

8- MRDC (Pin 7) 8 : هي إشارة أمر قراءة الذاكرة وهي إشارة خرج فعالة عند منطق منخفض. فهي تأمر الذاكرة بأن تضع البيانات على ناقلة البيانات لكي يقرأها المعالج الدقيق وتسمى هذه بعملية قراءة الذاكرة.

9- MWTC (Pin 9): وهي إشارة أمر الكتابة في الذاكرة وهي إشارة خرج فعالة عند منطق منخفض. فهي تأمر الذاكرة بكتابة البيانات الموجودة على ناقلة البيانات. وتسمى هذه بعملية كتابة الذاكرة.

10- AMEC (Pin 8) : وهي إشارة كتابة متقدمة في الذاكرة Advance Memory Write Command وهي إشارة خرج فعالة عند منطق منخفض. وتستخدم لتعطي ملحوظة مسبقة (مبكرة) للذاكرة بأن هناك عملية كتابة ستتم.

11- IORC (Pin 13) : وهي إشارة أمر قراءة الـ 1/0 وهي تشبه الإشارة MRDC إلا أنها تطبق على جهاز 1/0 فهي تخبر جهاز الـ 1/0 أن المعالج الدقيق بريد أن يقرأ البيانات من المعالج الدقيق يريد أن يكتب البيانات في الجهاز.

12- IOWC (Pin 11) : وهي إشارة أمر كتابة في الـ1/0 وهي تخبر جهاز الـ 1/0 بأن المعالج الدقيق يريد أن يكتب البيانات في الجهاز. تسمى هذه بعملية كتابة الـ 1/0 (1/0 Write operation).

13- AIOWC (Pin 12): وهي إشارة أمر كتابة متقدمة في الـ (Advance 1/0 write command) 1/0 وهي تشبه الإشارة AMWC: إلا أنها تطبق على جهاز 1/0 وهذه الإشارة تعطي ملحوظة مسبقة (مبكرة) لجهاز الـ1/0 بأن هناك عملية كتابة ستتم.

14- INTA (Pin 14): وهي إشارة اعتراف بالمقاطعة Interrupt Acknowledge وتستخدم لإخبار الجهاز الذي طلب المقاطعة بأن المعالج الدقيق قد قبل أو اعترف بطلب المقاطعة.

15- DT/R (Pin 4): وهي إشارة إرسال/استقبال البيانات Data Transmitt/Reciteve وتتحكم هذه الإشارة في اتجاه البيانات خلال المرسل/ المستقبل (Transceiver) فعندما يكون منطق هذه الإشارة عالي فإن هذا معناه أن المعالج الدقيق في حالة إرسال بيانات بينما عندما يكون منطقها منخفض فهذا يدل على أن المعالج الدقيق في حالة استقبال بيانات.

16- DEN (Pin 16) : وهي إشارة تمكين بيانات Data Enable وهي إشارة خرج فعالة عند منطق عالي. وتستخدم لتمكين مرسل/ مستقبل البيانات.

17- MCE/PDEN (Pin 17): وهي إشارة تمكين متبوع التتالي Master Cascade Enable (MCE) تشير هذه الإشارة ومعها إشارة IOB، عندما تكون ذات منطق منخفض لحاكم المقاطعة أثناء عملية مقاطعة بأن هناك عناوين متتالية ستقرأ. فيقوم حاكم الناقلة بضم عنوان المقاطعة (يسمى الموجه Vector) إلى ناقلة العناوين لخلق عنوان الخدمة. بينما تستخدم الإشارة Peripheral data enable (PDEN) ومعها إشارة IOB لتمكين مرسل/ مستقبل ناقلة الـ 1/0 bus transceiver) 1/0

18- ALE (Pin 6) وهي إشارة تمكين سقطة العناوين Address Latch Enable signal وهي إشارة خرج فعالة عند منطق عالي، وتقوم بتمكين سقطة العناوين.

مرة أخرى نعود لمخطط مكونات اللوحة الأم IBM PC-XT شكل 4-4 فنجد فوق رقاقة المعالج أي أقصى يمين أعلى اللوحة الأم نجد مفتاح يطلق عليه مفتاح التوصيف أو Configuration Switch.

تعليقات

إرسال تعليق